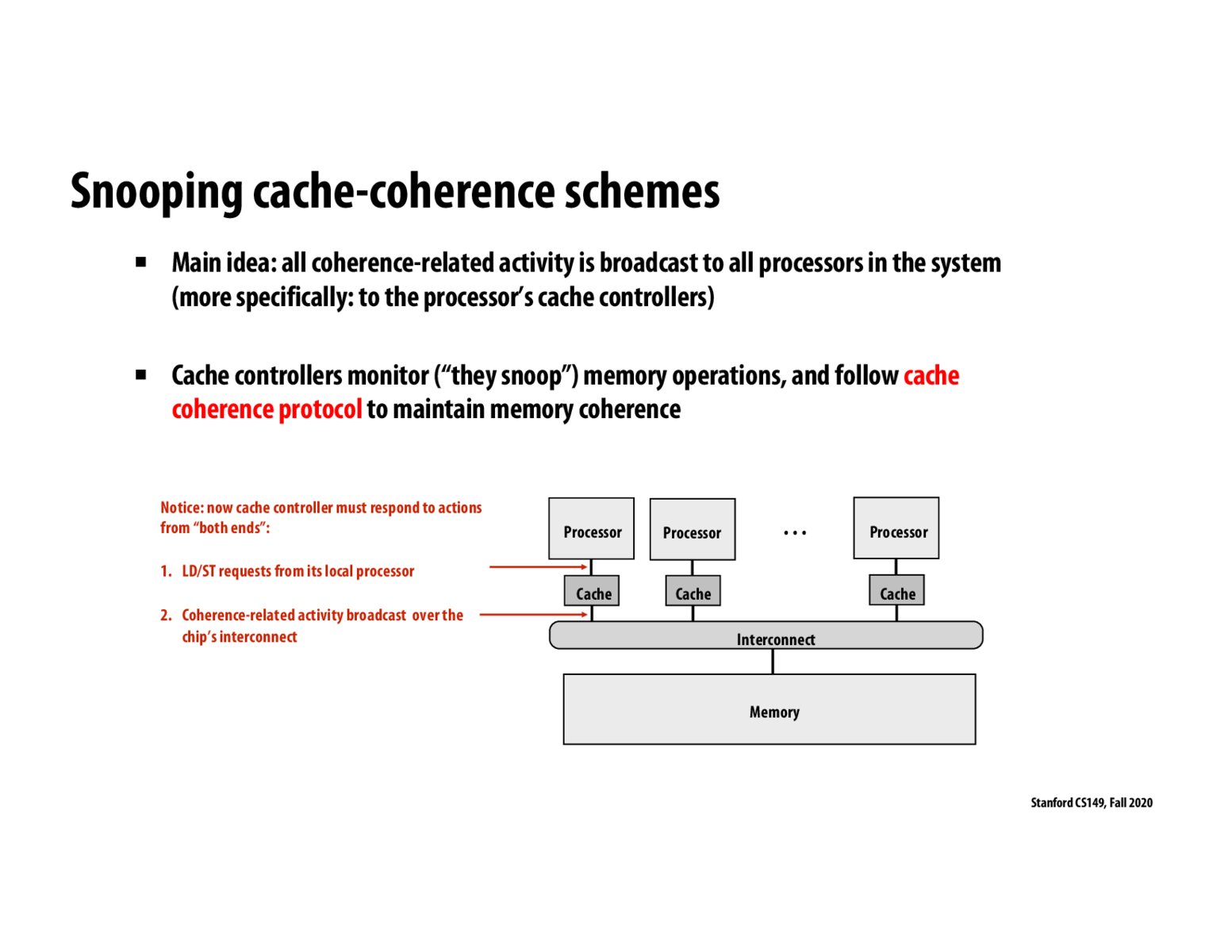

@ishangaur I believe the answer to your question is that the cache controllers manage everything. From the perspective of the processor (see slide 28), the only operations that it needs to perform are read (PrRd) and write (PrWr) operations. The cache controller listens to the interconnect for the other three coherence-related operations (BusRd, BusRdX, and BusWB) and is in charge of updating the state machine described on slide 29.

In a sense, every cache is telling every other cache what it is doing through an event notification to every other processor. And all the caches are then snooping at the other caches to see what they are doing. How do these notifications "snooping" between caches esp reading/writing at the same time work in implementation?

@parallelpower The snooping works because of Single-Writer, Multiple-Read (SWMR) where only processor rights to x and the number of processors reads to x. However, how does the notification system work telling all other caches something has been written and to read or snoop? Is a notify all done every time a cache writes, telling the other caches to snoop?

Please log in to leave a comment.

So when the cache controllers react to some memory operation they saw while snooping, does it take any work from the CPU to manage the state, or are the controllers able to manage everything?