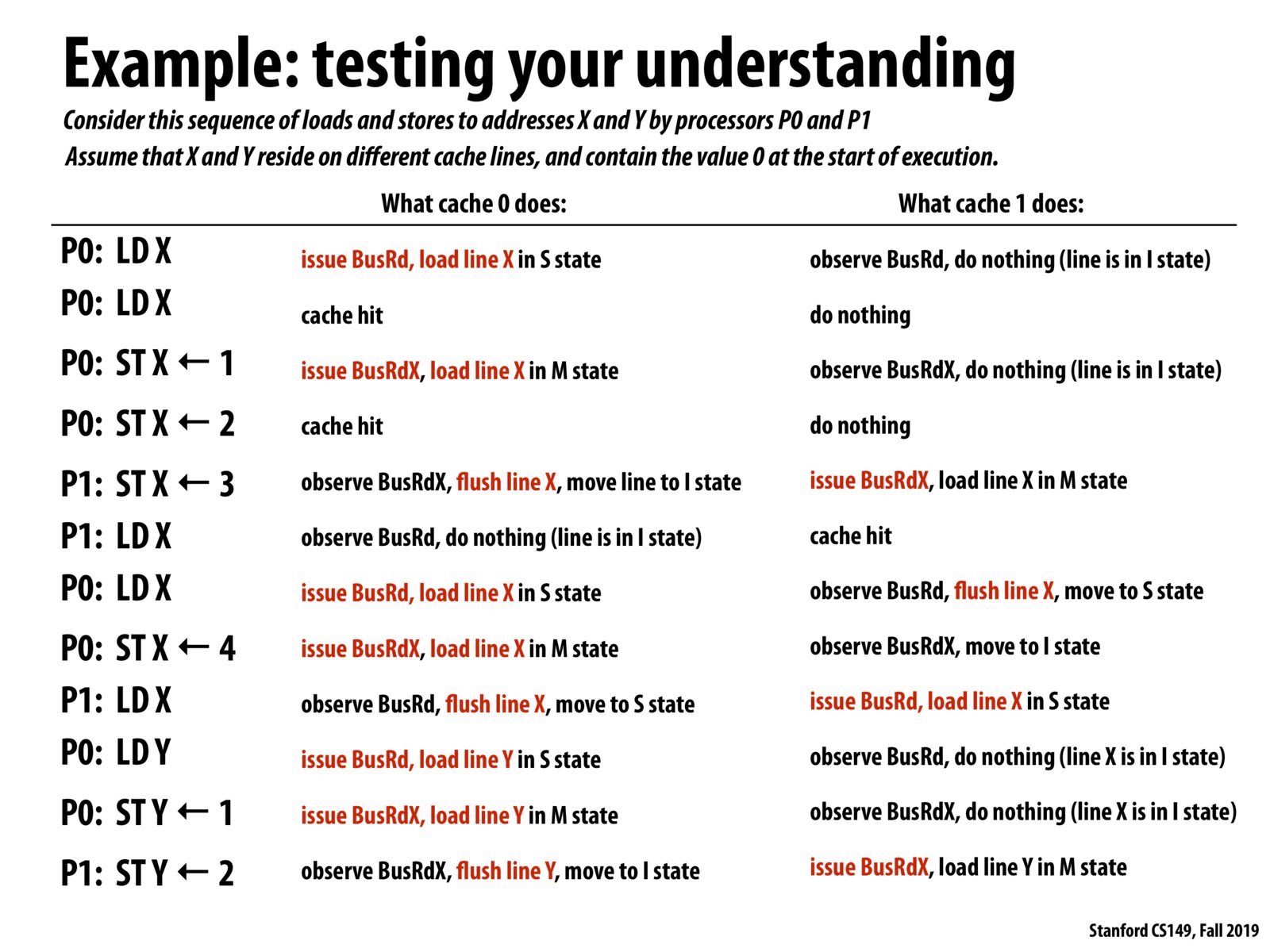

At the "P0: LD Y" step, why P1 says line X is in I state when at the last step, line X is still in S state in P1? Does P0 loading in Y affect P1's line X's state?

Should the last few lines be (line Y is in I state) instead of (line X is in I state)?

@suninhouse, I believe you are correct. Since the instruction stream on P0 is loading and operating upon Y, cache 1's actions would be determined by the state of that line per processor. Here, it makes sense that cache 1 does nothing during those instructions because line Y is in I state.

I agree. I think "line Y is in I state" makes more sense.

One source of confusion for me is that in this slide, it appears that a processor's cache line can stay in I state after a transition, even though the I state in the FSM doesn't have a transition to itself. Rather, in the case of a BusRd (P1 reads from same cache line), P0's line changes from I to S.

To answer my own question, this slide is correct. On a BusRd/BusRdX, a cache line in the Invalid state should stay in the Invalid state. The FSM has a transition from I to S that is labeled PrRd/BusRd, but it is just referring to the local processor doing a PrRd, which issues a BusRd that everyone sees. My misunderstanding was that the BusRd was remotely issued, but that is wrong -- Kayvon had colored the lines differently depending on which are locally triggered and which are remotely triggered. Thus, there is an implicit transition from I to itself on any remote BusRd or BusRdX.

Two questions: 1) At the very beginning (empty cache), do all processors view the cache line as in the I state?

2) How come on the 6th operation (P1: LD X where it gets a cache hit), the cache 0 controller observes a BusRd? Since P1 stays in the M state, I thought that no messages need to be broadcast?

Something I was contemplating is what happens when P1 wants to write to some address which is in the modified state in P2's cache. P1 sends the BusRdx out, which is intercepted by P2. My understanding of what happens next is that P2 sends the data from its cache to P1's cache and also writes back the data to memory using BusWb. So both actions occur in this particular scenario.

@tspint I'm sorry this is almost a week late, but let me try to answer your questions in case you were still wondering.

- With the way the MSI state machine was drawn in the previous slide, you're right in that the $-lines can be thought of as being in the I state. Alternatively, you could define a new "cold miss" state representing that a $-line isn't even in the $ (which is slightly different from being invalid and in the $). This state would have transitions directly to the S and M states, but not to the I state.

- I think this is a mistake in the slides. It should probably say "observe nothing and do nothing."

Please log in to leave a comment.

Important things to note here, perhaps more intuitively than in the MSI state transition:

1) Whenever a cache line is written, the processor who writes it moves to state M, while any other processor with the line in its cache moves to state I.

2) Whenever someone has a read cache miss, they move from state I to state S. 2b) Whenever someone has a write cache miss, they move from state I to state M.

3) Any processor in M state will flush to memory whenever another processor wants to read OR write the line.

4) Any processor in M reads or writes line without creating bus traffic.