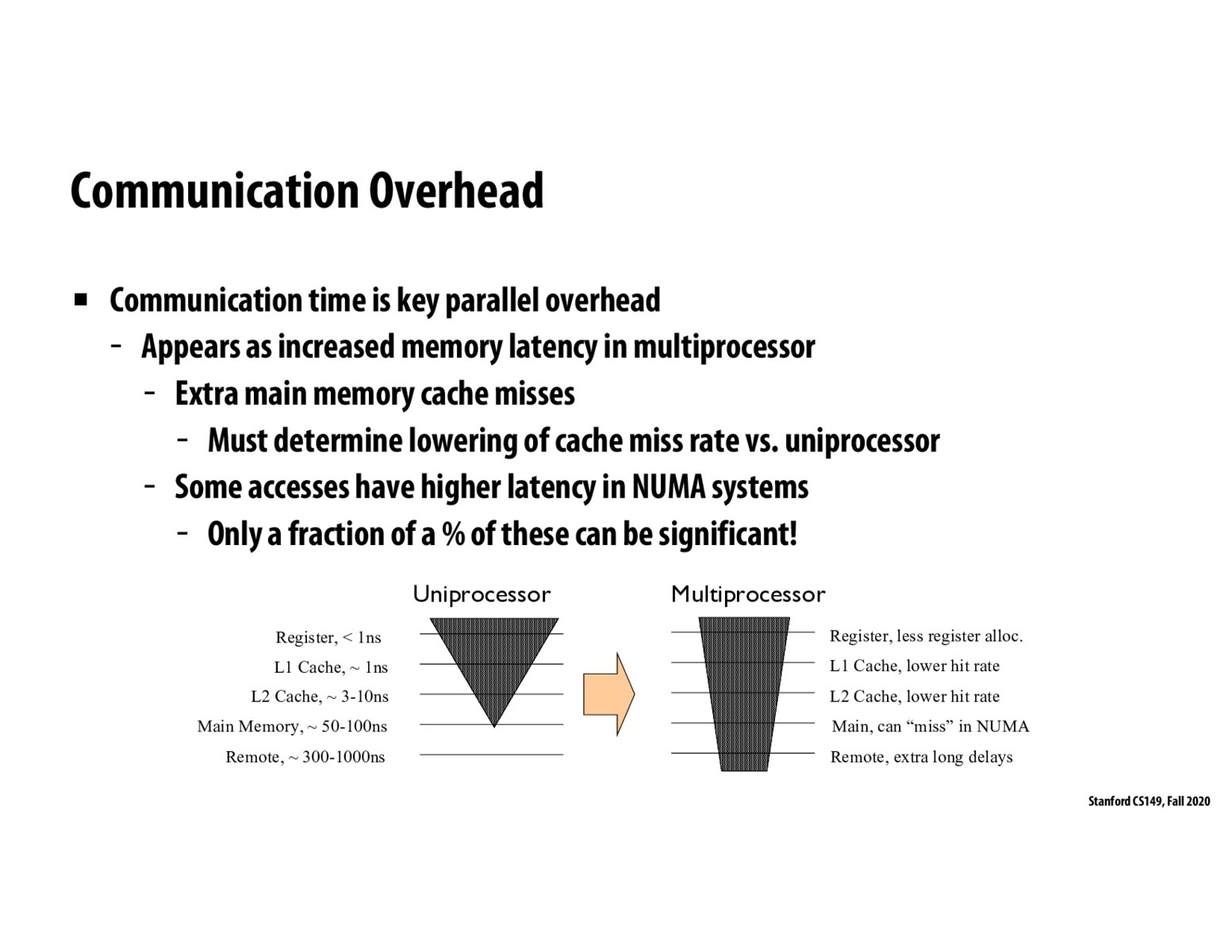

Does our discussion on cache coherence apply to both uniprocessor and multiprocessor scenarios and does this figure tell us the problem of maintaining cache coherence(resulting in extra cache misses) is exaggerated when we have a multiprocessor chip?

@suninhouse I believe it does. The purpose of the graph is meant to show how coherence communication overhead can turn what would normally be simple cache queries in a uniprocessor system to drawn out queries in a coherent mulltiprocessor system. The wider bottom would indicate a higher frequency of queries being dragged out.

@thread17 I don't believe that cache coherence is applies in a system with a single processor because cache coherence is primarily a problem with duplicated cache entries in the processor specific (L1, L2) caches of multicore machines. If there's no duplication of cache entries, as long as your system is memory consistent, you shouldn't have issues with your cache. I think the second part of your question is correct -- because cache coherence schemes have additional communication overhead (i.e. broadcasting, pinging 'directory' entries), we'll see worse cache latency more frequently in multiprocessor systems.

What is meant by "Main, can 'miss' in NUMA?" Is that just referring to the possibility that data in main memory could not be in the cache? Also, is "remote" here just "disk" (like an SSD or hard drive)?

Please log in to leave a comment.

Does the width of the graph represent frequency?