Back to Lecture Thumbnails

tp

l-henken

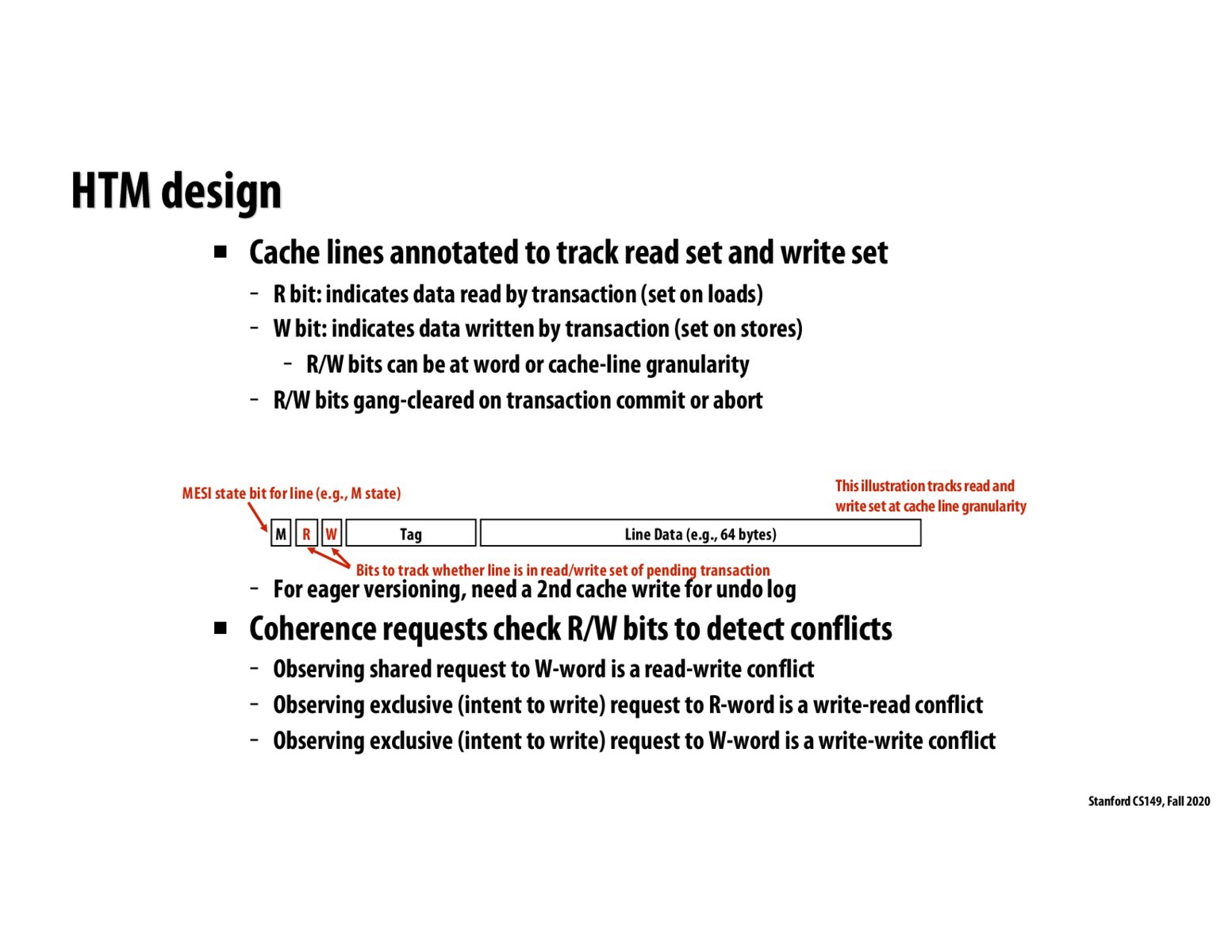

R/W bits can be cache-line or word granularity. If they are cache-line granular, TM commit and abort logic works easily with the cache coherency protocol and takes up less space. If they are word granular, false TM conflicts will be prevented.

jessiexu

- Since R/W are represented as a single bit and it can only track one transaction, what happens to the read and write set of other transactions that happen simultaneously?

- R/W bits gang-clearing at commit or abort is a huge overhead since cache needs to be modified again.

gpu

This might be a trivial question, but how is the MESI state encoded as a single bit here? Wouldn't we need at least 2 to convey the 4 possible states?

lfu

@gpu I'm curious about this as well. If it is only one bit, I'm assuming the state bit is used in conjunction with the R and W bit to determine the MESI state? I'm not completely clear on how that would work though.

haiyuem

@gpu I'm assuming it still uses 2 bits here for MESI. I'm curious about @jessiexu's 1st question as well...

Please log in to leave a comment.

Copyright 2020 Stanford University

If I understand correctly, HTM builds on top of cache coherence protocols by keeping all memory operations from a single transaction within the cache until it's time to commit. Then it uses the coherence protocol to validate the read set, invalidate other threads' cache lines if necessary, and commit the transaction all at once. If the read set is not validated or another thread performs a write and invalidates a cache line that our thread is using, then the transaction is aborted.