From the lecture about domain specific language, this shows that spatial targets performance and productivity and give up generality. Here, the productivity is making it easier for developers to design hardware accelerators using a high level language embedded in Scala. Just by choosing Scala, also makes it easier to program compared to C/C++. Spatial then provides abstractions for thinking about the underlying hardware.

Highlighting what David mentioned in class in the chat because I thought it was interesting. You run into a variant of the bin packing problem. You want to place parts of your code on the machine, but the farther apart the different parts of code are, the longer the wires and the lower the clock rate. Thus, you want to minimize where your code goes.

https://en.wikipedia.org/wiki/Bin_packing_problem

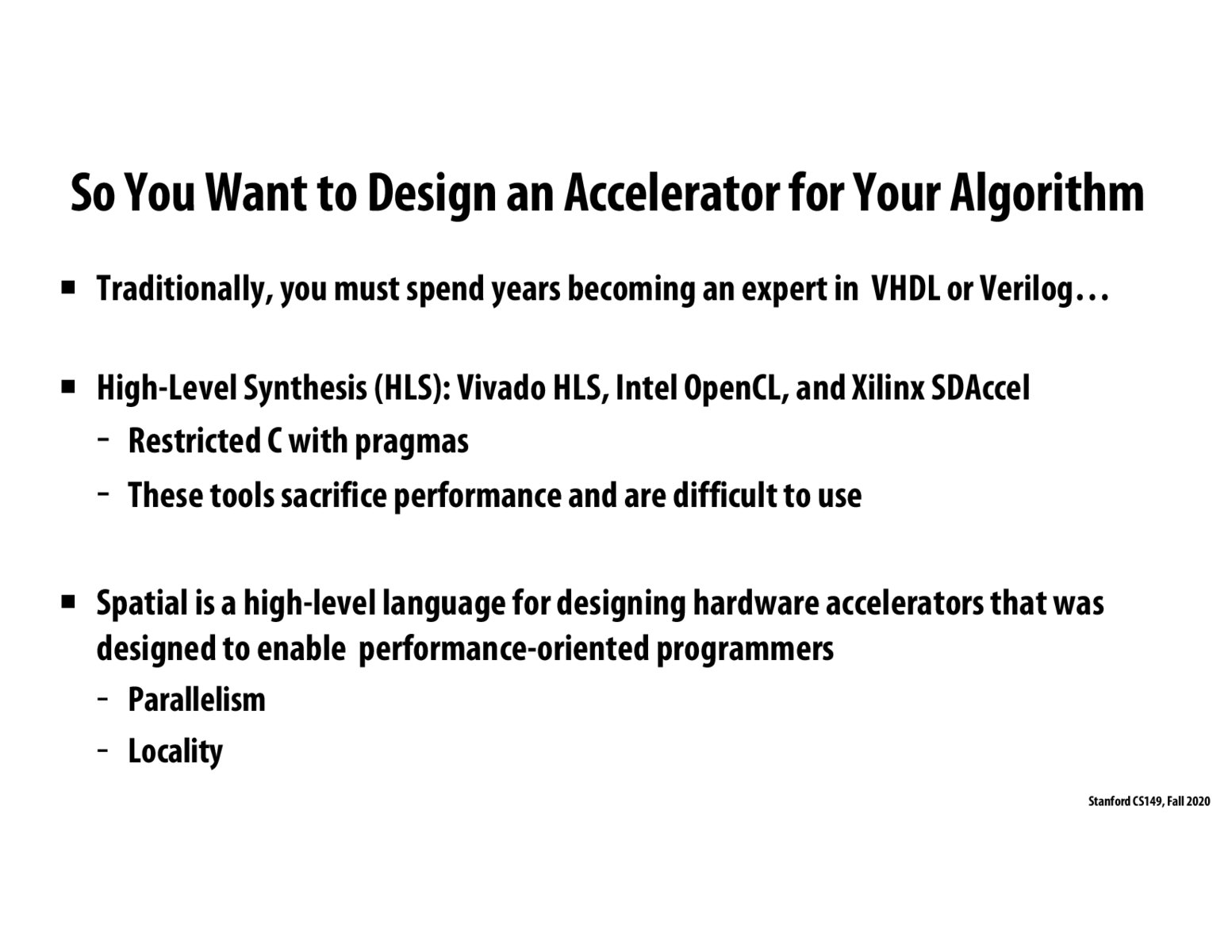

The idea behind high-level synthesis is to take a restricted set of C and use that to generate Verilog, which can then be used to program FPGAs. The problem with this is that in order to get high performance, you need to add a lot of pragmas, which can be hard to do.

Please log in to leave a comment.

Typically, in order to extract extra performance from an FPGA requires a huge amount of low-level knowledge to program the FPGA to optimally handle your specific workload (VDHL, Verilog). Spatial acts as a tool to make this FPGA design more accessible by providing a higher level language where programmers give descriptive information about the desired workload and performance optimizations desired. Spatial then given this descriptive information provides the programmer with information about the extracted performance and hardware design for their described workload.