Would it be accurate to think of acquiring the bus ownership as similar to acquiring a mutex? Only one cache can access it at a time, unless no one acquires ownership, such as exclusively using BusRd.

@cbfariasc Yes. Acquiring a mutex guarantees SWMR invariant, allowing only the writer that has the lock to modify the variable. I'm wondering where these states are stored though. Is it true that they are stored in the memory, and it's the cache controller's responsibility to set these flags?

Just curious, will the Invalidation state also influence the cache replacement policy such as LRU?

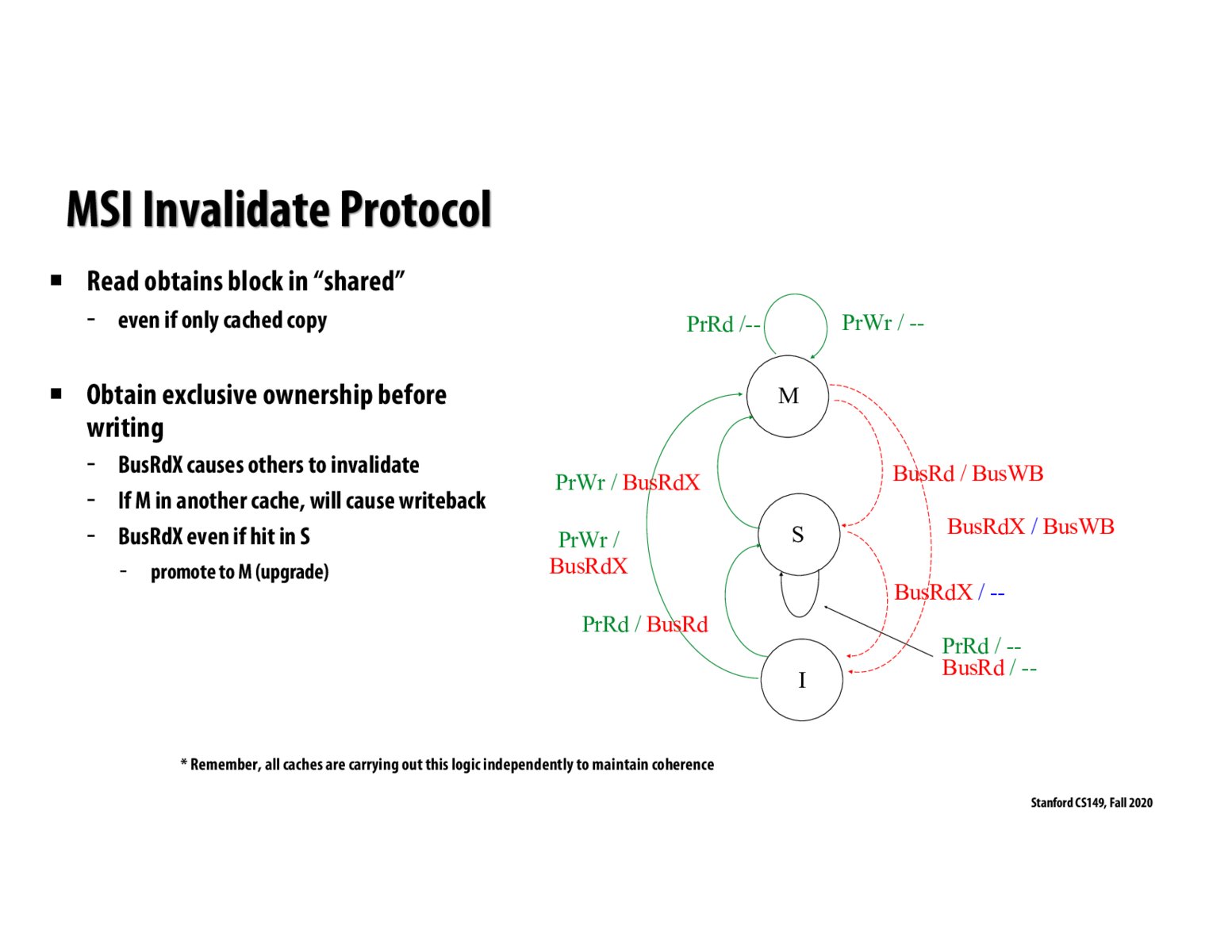

Something to note: not every memory operation generates bus traffic. For if a processor has a cache line in the shared state, it can write to or read from it all it wants without informing the other processors. Moreover, processors that have a cache-line in the invalid state ignore all bus traffic related to that cache-line.

Please log in to leave a comment.

How long does this take, and how many processors are usually involved? It seems laborious to, say, have all cache controllers reply that they aren't M before reading a value.