From what I got from lecture, I'm seeing that the main goal of cache coherence is to ensure that processor updates on a variable in their cache is properly propagated to all other processors when the same piece of data is accessed in subsequent reads.

@nickbowman thank you for the clarification. I guess this means that the HW implementation is free to choose any serial ordering that all the threads agree on.

Here is my stab at reformulating this definition in my own words:

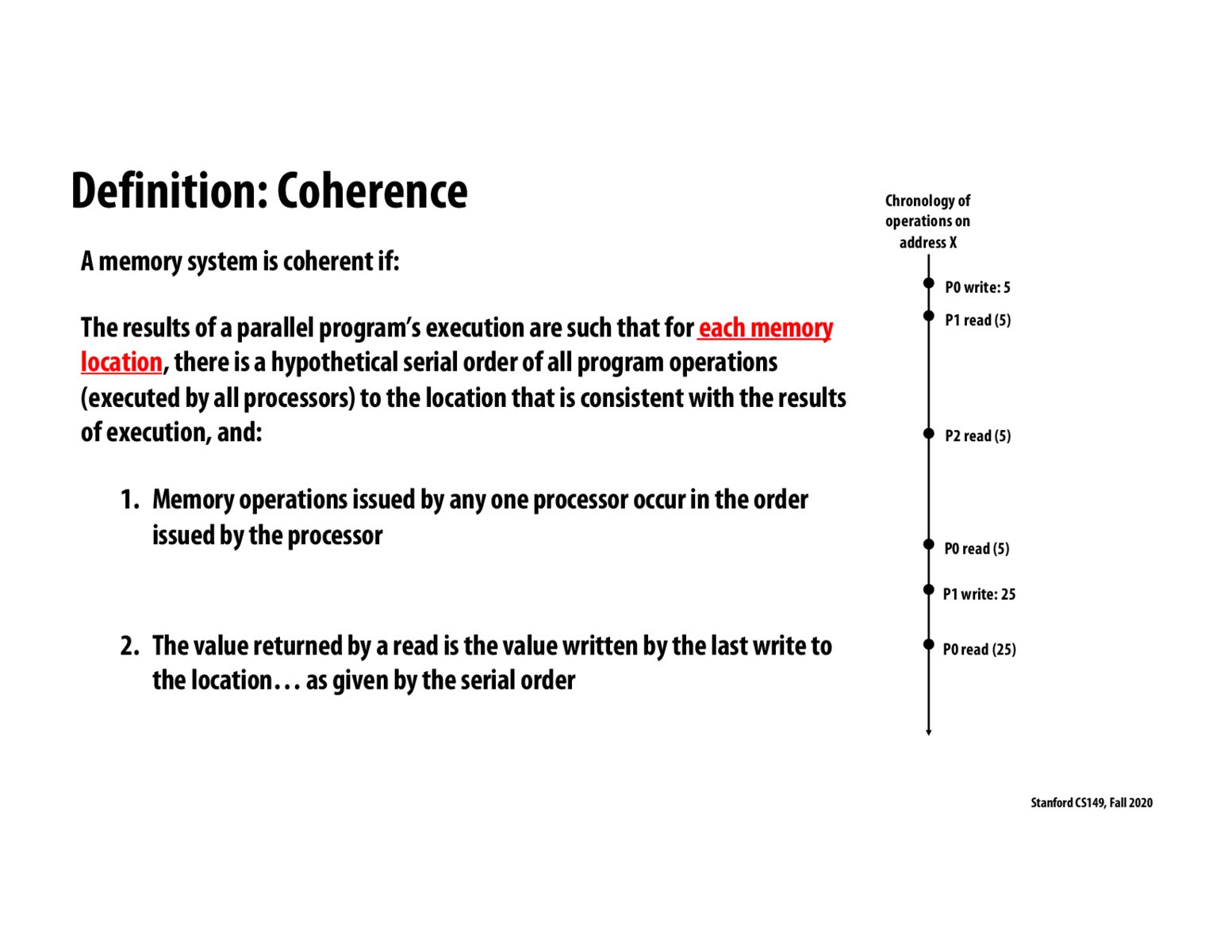

A coherent memory system is one that guarantees that when you execute a parallel program, everything you observe about the output is consistent with there being, for every memory address A, some hypothetical sequential order of read and write operations HSO_A that satisfies the following two properties:

- For every processor P, the read and write operations in HSO_A associated with P occur in program order for P.

- For every read operation R in HSO_A, the value read is equal to the value written by the last write operation W in HSO_A occurring before R.

Another way to interpret cache coherence is: would it perform the same as if there is no cache at all. Note that later there is another closely related but different concept called memory consistency, which is required on systems that do not even have cache and it is concerned with read and write of all locations.

Please log in to leave a comment.

Kayvon made the following clarification in the chat during the lecture: The key idea here is that all values observed by reads by all threads are consistent with SOME serial ordering (not any particular ordering is required, as any interleaving between the threads is possible as long as the results produced by all threads "agree" with that order -> consistent with the results of execution as stated in the slides).